7.3 I/O 方式

7.3.1 程序查询方式

特点:CPU 有“踏步”等待现象 CPU 与 I/O 串型工作。

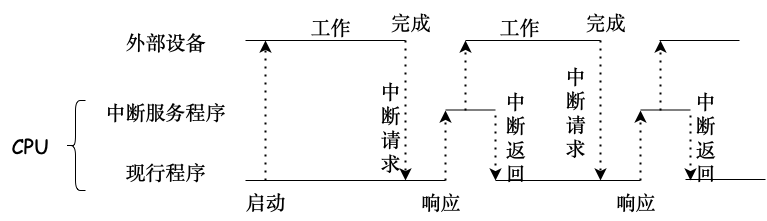

7.3.2 程序的中断方式

3.多重中断和中断屏蔽技术

7.3.3 DMA 方式

在 DMA 传送方式中,由外部设备向 DMA 控制器发出 DMA 请求信号,然后由 DMA 控制器向 CPU 发出总线请求信号。在 DMA 方式中,DMA 控制器在传送期间由总线控制权,这时 CPU 不能响应 I/O 中断。

DMA 方式只能用于数据传输。

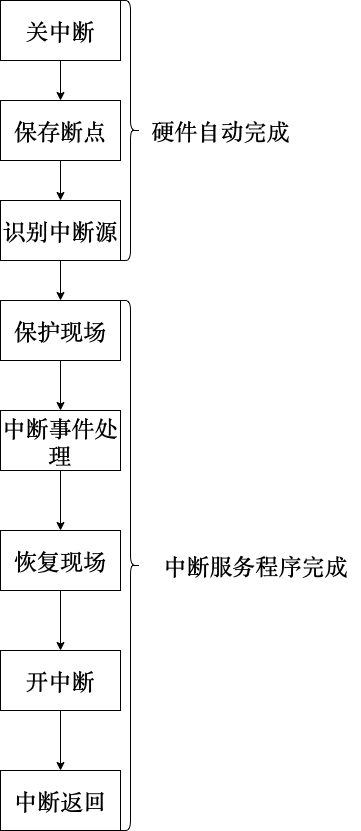

CPU 响应中断 3 个条件:

1.中断源有中断请求。

2.CPU 允许中断及开中断。

3.一条指令执行完毕,且没有更紧迫的任务。

假设计算机的主频为 500MHz,CPI 为 4.现有设备 A 和 B,其数据传输率分别为 2MB/s 和 40MB/s,对应 I/O 接口中各有一个 32 位数据缓冲寄存器。

(1) 若设备 A 采用定时 I/O 方式,每次输入/输出都至少执行 10 条指令。设备 A 最多间隔多长时间查询一次才不能丢失数据?CPU 用于设备 A 输入/输出占 CPU 总时间的百分比至少是多少?

设备 A 准备 32 位数据所用的时间为$4B/2MB=2us$,所以最多每隔 2us 查询一次。每秒查询次数至少是$1s/2us=5\times 10^{5}$,每秒查询用的时钟周期为$5\times 10^{5}\times 10\times 5=2\times 10^{7}$个时钟周期,占百分比$2\times 10^{7}/500M=4%$。

(2) 在中断 I/O 方式下,若每次中断响应和中断处理的总时钟周期数至少为 400,则设备 B 能否采用中断 I/O 方式?为什么?

中断响应和中断处理的时间为$400\times \left( 1/500M\right) =0.8us$,而 B 准备 32 位数据所用的时间为$4B/40MB=0.1us$,小于中断响应和中断处理时间,数据会被刷新,因此设备 B 不适合采用中断 I/O 方式。

(3) 若设备 B 采用 DMA 方式,每次 DMA 传送的数据块大小为 1000B,CPU 用于 DMA 预处理和后处理的总时钟周期数为 500,则 CPU 用于设备 B 输入/输出的时间占总时间的百分比最大是多少?

设备 B 每秒的 DMA 次数最多为$40MB/1000B=40000$,CPU 用于设备 B 输入/输出的时间最多为$40000\times 500=2\times 10^{7}$个时钟周期,占 CPU 总时间的百分比最大为$2\times 10^{7}/500M=4%$。

假设某计算机的 CPU 主频为 80MHz,CPI 为 4,平均每条指令访存 1.5 次,主存与 Cache 之间交换的块大小为 16B,Cache 命中率为 99%,存储器总线宽度为 32 位。请回答下列问题。

(1) 该计算机的 MIPS 数是多少?平均每秒 Cache 缺失的次数是多少?在不考虑 DMA 传送的情况下,主存带宽至少达到多少才能满足 CPU 的访存要求?

MIPS=80/4=20。$20\times 1.5\times 0.01=0.3M$次。$0.3M\times 16B=4.8MB/s$。

(2) 假定在 Cache 缺失的情况下访问主存时,存在 0.0005% 的缺页率,则 CPU 平均每秒产生多少次缺页异常?若页面大小为 4KB,每次缺页都需要访问磁盘,访问磁盘时 DMA 传送采用周期挪用方式,磁盘 I/O 接口的数据缓冲寄存器为 32 位,则磁盘 I/O 接口平均每秒发出的 DMA 请求次数至少是多少?

平均每秒产生的缺页中断 300000x0.0005%=1.5 次,1.5x4KB/4B=1.5K=1536

(3)CPU 和 DMA 控制器同时要求使用存储器总线时,哪个优先级更高?为什么?

CPU 和 DMA 控制器同时要求使用存储器总线时,DMA 请求优先级更高。因为 DMA 请求得不到及时响应,I/O 传输数据可能会丢失。

(4) 为提高性能,主存采用四体低位交叉存储模式,工作时每 1/4 个存储周期启动一个体。若每个题的存储周期为 50ns,则该主存能提供的最大带宽是多少?

$4x4B/50ns=320MB/s$

某计算机的 CPU 主频为 500MHz,CPI 为 5。假定某外设的数据传输率为 0.5MBps,采用中断方式与主机进行数据传送,以 32 位为传输单位,对应的中断程序包含 18 条指令,中断服务的其他开销相当于 2 条指令的执行时间。

(1) 在中断方式下,CPU 用于该外设 I/O 的时间占整个 CPU 时间的百分比时多少?

中断方式下,CPU 每次用于数据传送的时钟周期为$5x18+5x2=100$,外设每秒申请的中断次数为$0.5MB/4B=125000$。

1s 内用于中断的开销为$100x125000=12500000=12.5M$个时钟周期。

CPU 用于外设 I/O 的时间占整个 CPU 时间的百分比为$12.5M/500M=2.5%$

(2) 当该外设的数据传输率达到 5MBps 时,改用 DMA 方式传送数据。假定每次 DMA 传送块大小为 5000B,且 DMA 预处理和后处理的总开销为 500 个时钟周期,则 CPU 用于该外设 I/O 的时间占整个 CPU 时间的百分比时多少(假设 DMA 与 CPU 之间没有访存冲突)?

当外设数据传输率提高到 5MBps 时,改用 DMA 方式传送,每次 DMA 传送 5000B,1s 内需产生的 DMA 处理的总开销为 1000x500=500000=0.5M 个时钟周期。

CPU 用于外设 I/O 的时间占整个 CPU 时间的百分比为 0.5M/100M=0.1%