3.6 虚拟存储器

3.6.1 虚拟存储器的基本概念

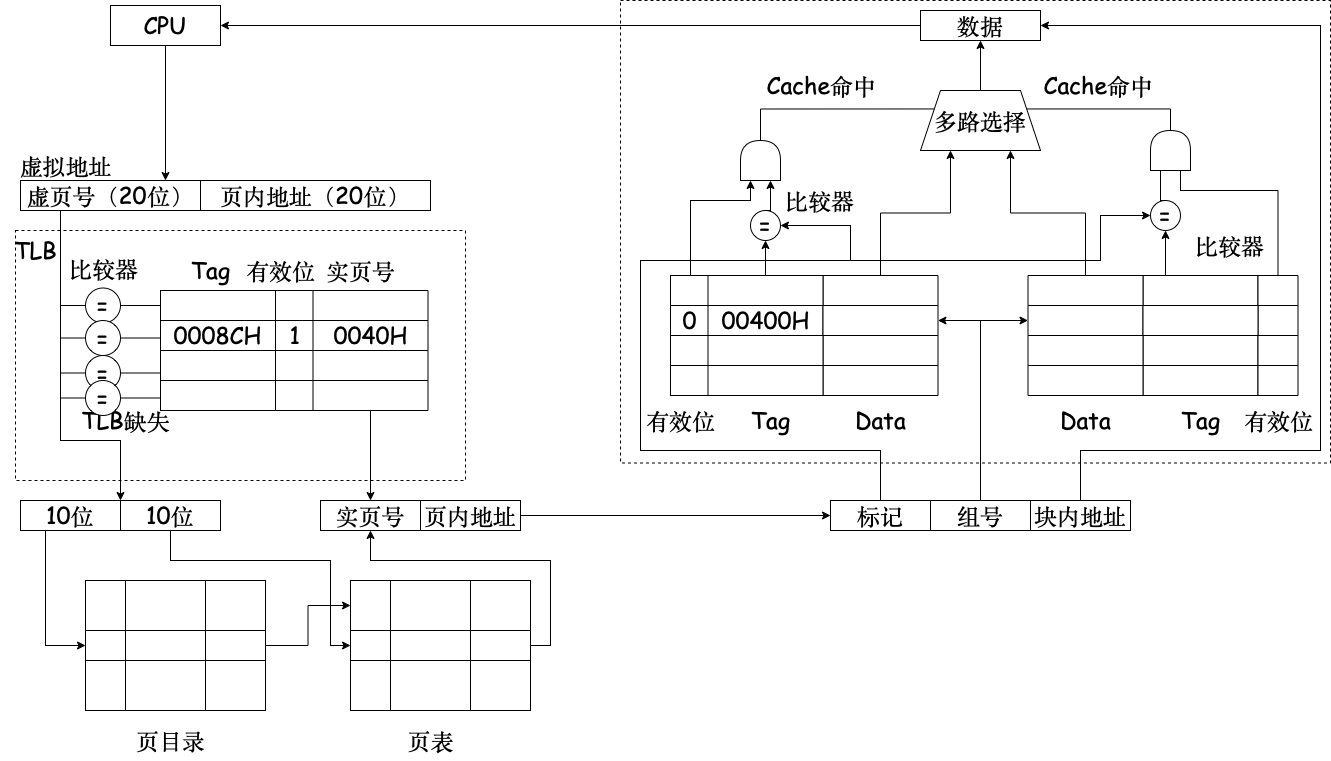

主存和辅存共同构成了虚拟存储器。

由于缺页而访问主存的代价很大,为了提高命中率,虚拟存储采用全相联映射和回写法。

Cache 是主存的一部分副本,TLB 是 Page(页表)的副本。

3.6.2 页式虚拟存储器

若计算机主存地址为 32 位,按字节编址,某 Cache 的数据区容量为 32KB,主存块大小为 64B,采用 32 路组相联映射方式,该 Cache 中比较器的个数和位数分别为?

| Tag 标记 | 组号 | 块内地址 |

|---|---|---|

| 20 位 | 6 位 | 6 位 |

在同时具有 TLB 和 Cache 的系统,CPU 发出访存命令,先查找对应的 Cache 块。